功能

PLECS PIL (PROCESSOR-IN-LOOP)

PLECS PIL 在環處理器與 PLECS Standalone 或 PLECS Blockset 模擬一個完整的解決方案。 PLECS PIL 可以在真實的微控制執行代碼,將在 PLECS 模型的虛擬環境中驗證,並驗證控制碼的缺陷。

PLECS PIL 的元件庫支持且應用於電力變流器的不同嵌入式處理器類型,同時支援多種通信接口來連接硬體和電路設計模組。

為什麼要使用PIL?

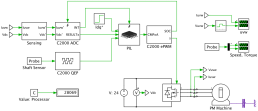

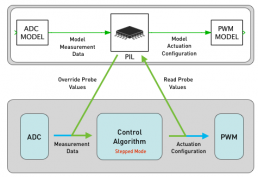

比起工程師開發嵌入式控制算法時,把代碼在設計電路中進行測試,PIL 將控制算法直接在微控制器上執行。模擬軟體中功率變流器量模型的量測值以數字的方式被傳到嵌入式控制算法的輸入端,而控制算法的輸出值,則被反饋回模擬軟體來驅動模擬環境。這種方式可以檢查出代碼的缺陷,如溢出等。PIL 模擬同時可以用於監測分析多進程控制算法的潛在問題,如不合理的資源分配。

運作原理

- 控制算法執行一個週期

- 模擬過程改寫嵌入式處理器控制代碼的輸入變量,如電流電壓量測值。

- 控制代碼的輸出值,如 PWM 外設的寄存器設定值,被傳送到 PLECS 模擬環境中。

PIL 支援的嵌入式處理器

1. TI C2000系列(包括最新的 Delfino 雙核 DSP)

2. ST STMF4系列

3. Microchip dsPIC33F ( MC 版本)